I’ve done a little work on creating a new target for this board. This is a WIP and untested.

Goal is to have bidirectional DShot support, DMA on USART1 (on-board ELRS, uses CRSF protocol), USART3 (for GPS), and UART6. I have a timer assigned to the LED_STRIP pin, but don’t know if TIM1_UP is sufficient for WS2812 use.

What is the correct value of HAL_STORAGE_SIZE for 8M onboard flash?

hwdef.dat:

# hw definition file for processing by chibios_pins.py

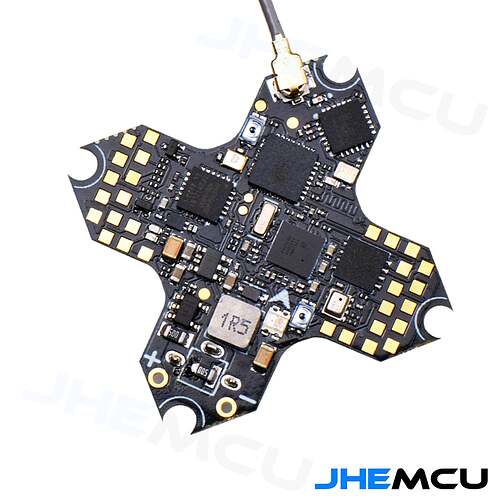

# JHEMCU GSF405A

# With F405 MCU, MPU6000 IMU and 7456 series OSD

# Based on Mamba F405 from jeanphilippehell

@ thanks to betaflight for pin information

MCU STM32F4xx STM32F405xx

# board ID for firmware load

APJ_BOARD_ID 1060

# crystal frequency

OSCILLATOR_HZ 8000000

# board voltage

STM32_VDD 330U

define STM32_ST_USE_TIMER 4

define CH_CFG_ST_RESOLUTION 16

# order of I2C buses

I2C_ORDER I2C1

# order of UARTs (and USB)

# this order follows the labels on the board

SERIAL_ORDER OTG1 USART1 USART2 USART3 UART4 EMPTY USART6

# The pins that USB is connected on

PA11 OTG_FS_DM OTG1

PA12 OTG_FS_DP OTG1

PC5 VBUS INPUT OPENDRAIN

# USART1 (DMA) - wired to on-board ELRS receiver - need DMA for CRSF protocol

PB6 USART1_TX USART1

PA10 USART1_RX USART1

# Alt config to allow PPM on RX1

#PA10 TIM1_CH3 TIM1 RCININT PULLDOWN ALT(1)

# USART2

PD5 USART2_TX USART2 NODMA

PD6 USART2_RX USART2 NODMA

# USART3 (DMA) - Use for GPS as it is close to I2C pins.

PB10 USART3_TX USART3

PB11 USART3_RX USART3

# UART4

PA0 UART4_TX UART4

PA1 UART4_RX UART4 NODMA

# USART6 (DMA)

PC6 USART6_TX USART6

PC7 USART6_RX USART6

# ADC

PC3 BAT_VOLT_SENS ADC1 SCALE(1)

PC0 RSSI_IN ADC1

PC2 BAT_CURR_SENS ADC1 SCALE(1)

# Motor outputs on AIO ESC

PB0 TIM3_CH3 TIM3 PWM(1) GPIO(50)

PB1 TIM3_CH4 TIM3 PWM(2) GPIO(51) BIDIR

PA3 TIM5_CH4 TIM5 PWM(3) GPIO(52) BIDIR

PA2 TIM5_CH3 TIM5 PWM(4) GPIO(53)

# Board LEDs

PC14 LED1 OUTPUT LOW GPIO(1)

#PC14 LED2 OUTPUT LOW GPIO(2)

define HAL_GPIO_A_LED_PIN 1

#define HAL_GPIO_B_LED_PIN 2

# Assign timer to LED_STRIP

#PA9 LED_EXT1 OUTPUT GPIO(30)

PA9 TIM1_CH2 TIM1 PWM(5) GPIO(54)

DMA_PRIORITY SPI3*

DMA_NOSHARE USART1*

# Buzzer

PC13 BUZZER OUTPUT GPIO(80) LOW

define HAL_BUZZER_PIN 80

define HAL_BUZZER_ON 1

define HAL_BUZZER_OFF 0

# I2C1

PB8 I2C1_SCL I2C1

PB9 I2C1_SDA I2C1

# SPI1 - Internal IMU

PB12 MPU6000_CS CS

PA5 SPI1_SCK SPI1

PA6 SPI1_MISO SPI1

PA7 SPI1_MOSI SPI1

# SPI2 - none

#PB13 SPI2_SCK SPI2

#PB14 SPI2_MISO SPI2

#PB15 SPI2_MOSI SPI2

# SPI3 - OSD + 8MB flash

PC10 SPI3_SCK SPI3

PC11 SPI3_MISO SPI3

PC12 SPI3_MOSI SPI3

# OSD max7456

PB14 OSD_CS CS

# Dataflash 8MB on-board

PB3 FLASH_CS CS

# SPI Device table

SPIDEV mpu6000 SPI1 DEVID1 MPU6000_CS MODE3 1*MHZ 4*MHZ

SPIDEV dataflash SPI3 DEVID2 FLASH_CS MODE3 32*MHZ 32*MHZ

SPIDEV osd SPI3 DEVID3 OSD_CS MODE0 10*MHZ 10*MHZ

# One IMU rotated in yaw

IMU Invensense SPI:mpu6000 ROTATION_YAW_180

# Probe for I2C BMP280, but allow init on board variants without onboard baro too

BARO BMP280 I2C:0:0x76

define HAL_PROBE_EXTERNAL_I2C_BAROS

define HAL_BARO_ALLOW_INIT_NO_BARO

# no built-in compass, but probe the i2c bus for all possible

# external compass types

define ALLOW_ARM_NO_COMPASS

define HAL_COMPASS_DEFAULT HAL_COMPASS_NONE

define HAL_PROBE_EXTERNAL_I2C_COMPASSES

define HAL_I2C_INTERNAL_MASK 0

define HAL_COMPASS_AUTO_ROT_DEFAULT 2

# enable logging to dataflash

define HAL_LOGGING_DATAFLASH

#Is this correct for 8M onboard flash?

define HAL_STORAGE_SIZE 7168

STORAGE_FLASH_PAGE 1

# flash size

FLASH_SIZE_KB 1024

# reserve 16k for bootloader and 32k for flash storage

FLASH_RESERVE_START_KB 48

# define default battery setup

define HAL_BATT_VOLT_PIN 11

define HAL_BATT_CURR_PIN 13

define HAL_BATT_VOLT_SCALE 11

define HAL_BATT_CURR_SCALE 17

# Analog RSSI pin (also could be used as analog airspeed input)

define BOARD_RSSI_ANA_PIN 1

# Setup for OSD

define OSD_ENABLED 1

define HAL_OSD_TYPE_DEFAULT 1

# Font for OSD

ROMFS_WILDCARD libraries/AP_OSD/fonts/font*.bin

hwdef.txt (3.5 KB)

hwdef.h

hwdef.h (56.5 KB)

DMA Assignments snippet:

// auto-generated DMA mapping from dma_resolver.py

#define STM32_ADC_ADC1_DMA_STREAM STM32_DMA_STREAM_ID(2, 4)

#define STM32_ADC_ADC1_DMA_CHAN 0

#define STM32_I2C_I2C1_RX_DMA_STREAM STM32_DMA_STREAM_ID(1, 5)

#define STM32_I2C_I2C1_RX_DMA_CHAN 1

#define STM32_I2C_I2C1_TX_DMA_STREAM STM32_DMA_STREAM_ID(1, 6) // shared TIM5_UP,I2C1_TX

#define STM32_I2C_I2C1_TX_DMA_CHAN 1

#define STM32_SPI_SPI1_RX_DMA_STREAM STM32_DMA_STREAM_ID(2, 0)

#define STM32_SPI_SPI1_RX_DMA_CHAN 3

#define STM32_SPI_SPI1_TX_DMA_STREAM STM32_DMA_STREAM_ID(2, 3)

#define STM32_SPI_SPI1_TX_DMA_CHAN 3

#define STM32_SPI_SPI3_RX_DMA_STREAM STM32_DMA_STREAM_ID(1, 0)

#define STM32_SPI_SPI3_RX_DMA_CHAN 0

#define STM32_SPI_SPI3_TX_DMA_STREAM STM32_DMA_STREAM_ID(1, 7)

#define STM32_SPI_SPI3_TX_DMA_CHAN 0

#define STM32_TIM_TIM1_UP_DMA_STREAM STM32_DMA_STREAM_ID(2, 5)

#define STM32_TIM_TIM1_UP_DMA_CHAN 6

#define STM32_TIM_TIM3_CH4_DMA_STREAM STM32_DMA_STREAM_ID(1, 2) // shared TIM3_UP,TIM3_CH4

#define STM32_TIM_TIM3_CH4_DMA_CHAN 5

#define STM32_TIM_TIM3_UP_DMA_STREAM STM32_DMA_STREAM_ID(1, 2) // shared TIM3_UP,TIM3_CH4

#define STM32_TIM_TIM3_UP_DMA_CHAN 5

#define STM32_TIM_TIM5_CH4_DMA_STREAM STM32_DMA_STREAM_ID(1, 3) // shared USART3_TX,TIM5_CH4

#define STM32_TIM_TIM5_CH4_DMA_CHAN 6

#define STM32_TIM_TIM5_UP_DMA_STREAM STM32_DMA_STREAM_ID(1, 6) // shared TIM5_UP,I2C1_TX

#define STM32_TIM_TIM5_UP_DMA_CHAN 6

#define STM32_UART_UART4_TX_DMA_STREAM STM32_DMA_STREAM_ID(1, 4)

#define STM32_UART_UART4_TX_DMA_CHAN 4

#define STM32_UART_USART1_RX_DMA_STREAM STM32_DMA_STREAM_ID(2, 2)

#define STM32_UART_USART1_RX_DMA_CHAN 4

#define STM32_UART_USART1_TX_DMA_STREAM STM32_DMA_STREAM_ID(2, 7)

#define STM32_UART_USART1_TX_DMA_CHAN 4

#define STM32_UART_USART3_RX_DMA_STREAM STM32_DMA_STREAM_ID(1, 1)

#define STM32_UART_USART3_RX_DMA_CHAN 4

#define STM32_UART_USART3_TX_DMA_STREAM STM32_DMA_STREAM_ID(1, 3) // shared USART3_TX,TIM5_CH4

#define STM32_UART_USART3_TX_DMA_CHAN 4

#define STM32_UART_USART6_RX_DMA_STREAM STM32_DMA_STREAM_ID(2, 1)

#define STM32_UART_USART6_RX_DMA_CHAN 5

#define STM32_UART_USART6_TX_DMA_STREAM STM32_DMA_STREAM_ID(2, 6)

#define STM32_UART_USART6_TX_DMA_CHAN 5

// Mask of DMA streams which are shared

#define SHARED_DMA_MASK ((1U<<STM32_DMA_STREAM_ID(1,2))|(1U<<STM32_DMA_STREAM_ID(1,3))|(1U<<STM32_DMA_STREAM_ID(1,6)))

// generated UART DMA configuration lines

#define STM32_USART1_RX_DMA_CONFIG true, STM32_UART_USART1_RX_DMA_STREAM, STM32_UART_USART1_RX_DMA_CHAN

#define STM32_USART1_TX_DMA_CONFIG true, STM32_UART_USART1_TX_DMA_STREAM, STM32_UART_USART1_TX_DMA_CHAN

#define STM32_USART2_RX_DMA_CONFIG false, 0, 0

#define STM32_USART2_TX_DMA_CONFIG false, 0, 0

#define STM32_USART3_RX_DMA_CONFIG true, STM32_UART_USART3_RX_DMA_STREAM, STM32_UART_USART3_RX_DMA_CHAN

#define STM32_USART3_TX_DMA_CONFIG true, STM32_UART_USART3_TX_DMA_STREAM, STM32_UART_USART3_TX_DMA_CHAN

#define STM32_UART4_RX_DMA_CONFIG false, 0, 0

#define STM32_UART4_TX_DMA_CONFIG true, STM32_UART_UART4_TX_DMA_STREAM, STM32_UART_UART4_TX_DMA_CHAN

#define STM32_USART6_RX_DMA_CONFIG true, STM32_UART_USART6_RX_DMA_STREAM, STM32_UART_USART6_RX_DMA_CHAN

#define STM32_USART6_TX_DMA_CONFIG true, STM32_UART_USART6_TX_DMA_STREAM, STM32_UART_USART6_TX_DMA_CHAN

// generated SPI DMA configuration lines

#define STM32_SPI_SPI1_DMA_STREAMS STM32_SPI_SPI1_TX_DMA_STREAM, STM32_SPI_SPI1_RX_DMA_STREAM

#define STM32_SPI_SPI3_DMA_STREAMS STM32_SPI_SPI3_TX_DMA_STREAM, STM32_SPI_SPI3_RX_DMA_STREAM

#define HAL_PWM_COUNT 5